# Introduction to INTEL X-86 Family

Probable marks: 4

### Scope of the syllabus :-

- Introduction to advanced microprocessors

- Introduction to X-86 family and study of major attributes of the X-86 family processors.

- Programming model of X-86 family of microprocessors.

# Q.1 Draw a block diagram of 8086 and explain it.

# Ans. :

200 SD E.C. 7

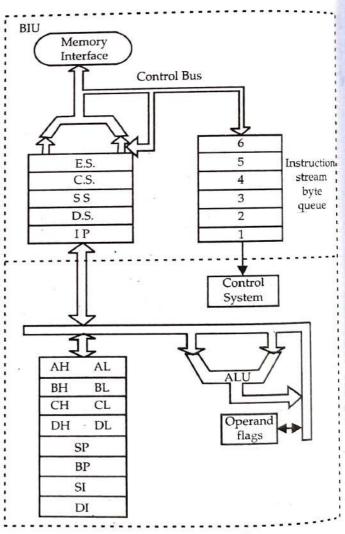

- As shown in the block diagram, the 8086 C.P.U. is divided into two independent functional parts :

- 1. Bus Interface Unit (B.I.U.)

- 2. Execution Unit (E.U.)

- The B.I.U. functional part contains queue, segment registers and instruction pointer.

- Execution unit (E.U.) contains flag register, general purpose registers, stack pointer register and other pointers, index registers.

Fig. 3.1

# Q.2 Explain in brief 8086 architecture.

Ans.: The 8086 C.P.U. is divided into two independent functional parts :

- I) Bus Interface Unit (B.I.U.)

- II) Execution Unit (E.U.)

# I. Bus Interface Unit (B.I.U.) :

The B.I.U. sends address, fetches instruction from memory, reads data from ports/memory and writes data to ports/memory. In other word, B.I.U. handles transfer of data and address on buses for execution unit. It consists of following parts :

- (a) Queue : To speed up execution of program, B.I.U. fetches 6 instruction bytes ahead of time from memory and stores them for E.U. in the FIFO register, called queue.

- (b) Segment registers : B.I.U. contains following 16-bit segment registers :

- i) Extra segment (E.S.)

- ii) Code segment (C.S.)

- iii) Stack segment (S.S.)

- iv) Data segment (D.S.)

These 16-bit segment registers are used to store 16-bit starting address of memory segment.

(c) Instruction pointer (I.P.) : The code segment (C.S.) register holds 16-bit starting address of segment, from which B.I.U. is fetching instruction code bytes. The IP register holds 16-bit address of next code byte within code segment.

#### II. Execution Unit (E.U.) :

Execution unit of 8086 tells B.I.U. where to fetch instructions or data, decodes instruction and executes them. The following sections describe functional part of E.U.:

- (a) Flag register : Flag is a flip-flop, which indicate some condition. The 8086 has 16-bit flag register with 9-active flags.

- (b) General purpose registers : 8086 has 8 general purpose registers, labelled AH, AL, BH, BL, CH, CL, DH and DL. These registers can be used individually for temporary storage of 8-bit data. The AL register is also called as accumulator. These registers in certain pairs can be used as 16-bit registers. These pairs are AH and AL (AX), BH and BL (BX), CH and CL (CX), DH and DL (DX).

- (c) Stack pointer : The 8086 allows us to set 64KB of memory as stack. The 16-bit starting address of stack is stored in stack pointer.

# Q.3 Explain any two microprocessors in X-86 family in brief.

OR Explain the following microprocessors in Intel's X-86 family. (Oct. 04; March 18) Ans. :

- I) 8086 :

- 1) 8086 is a **16-bit** microprocessor, introduced by INTEL in 1978.

- 2) It was designed to be used as C.P.U. in microcomputer system. It's A.L.U., internal registers can work with 16 binary bits at a time.

- 3) 8086 has 16-bit data bus and 20-bit address bus, so that it can address a  $phy_{Sica}$  memory of  $2^{20} = 1048576 = 1$  M Byte memory locations.

- 4) The least significant 8 bits of address bus are passed on same eight lines as that 0 data bus. This bus is known as multiplexed bus.

- 5) In 8086, words are stored in two consecutive bytes. If first byte of word has even address, then 8086 can read it in single operation. Else, it requires two operations.

- 6) This processor supports multiplication and division operations.

- 7) The 80186 is an improved version of 8086. In addition to 16-bit C.P.U., it has programmable peripheral (I/O) devices integrated in same package. Instruction set of 80186 is superset of instruction set of 8086.

#### II) 80286 :

- 1) 80286 is a **16-bit** microprocessor, introduced in 1982. This advanced version of 80% is specially designed to be used as a C.P.U. in multiuser/multitasking operating systems.

- 2) 80286 has 16-bit data bus and 24-bit address bus.

- In 1984, IBM introduced PC/AT (Personal Computer/Advanced Technology) version of its PC using 80286.

- 4) 286 was having real and protected modes of operation. In real mode, the processor can address only 1 Mbyte of memory, whereas in protected mode it can address 16 Mbytes of memory.

- 5) Another new feature was the ability to work upto 1 Gbyte of virtual memory and yet another feature was added hardware multitasking.

- 6) The program written for 8086 can run on 80286, operating in its real address mode.

#### III) 80386:

#### (July 2018)

- 1) The INTEL's 80386 is a 32-bit microprocessor introduced in 1985.

- 2) . 80386 is a logical extension of 80286. It is more highly pipelined.

- 3) The instruction set of 80386 is a superset of other members of 8086 family.

- 4) It has 32-bit data bus and 32-bit nonmultiplexed address bus. It can address a physical memory of 2<sup>32</sup> i.e.' 4 Gbytes. The 80386 memory management allows it to address 2<sup>46</sup> or 64 Tbytes.

- 5) The 386 can be operated in one of the following memory management modes :

- i) Paged mode

- ii) Non-paged mode.

- 6) When operated in paged mode, the 386 switches the paging unit then after the segment unit. The paging unit allows memory pages of 4 kB each to be swapped in and out from disk. In non-paged mode, memory management unit operates very similar to the 286.

- Virtual addresses are represented with selected components and an offsel component as they are with 80286.

#### 80486: [V)

TPS Computer Science - II

- Intel's 80486 is a 32-bit microprocessor. It was introduced in 1989. 1)

- It has 32-bit address bus and 32-bit data bus. 2)

- The 486 is basically a large integral circuit which contains a fast built-in, a math 3) coprocessor, a memory management unit (M.M.U.), and an 8 kbyte cache memory.

- 80486 has DX and SX versions. 4)

- All 486 processors have 32-bit data bus. SX version does not have on chip-numeric 5) coprocessor.

- The 486 achieves its high speed operation from its faster clock speeds, internal pipe 6) lined architecture and the use of reduced instruction set computing (RISC) to speed up the internal microcode.

- 486 also has 486 DX2 and 486 DX4 versions, with double and triple clock speed. 7)

#### Pentium or 80586 : OR V)

# Explain the main features of a pentium processor.

- Pentium is a 64 bit microprocessor, introduced in 1993. 1)

- It has 64 bit data bus and 32-bit address bus. The use of super scalar architecture 2) incorporates a dual-pipe lined processor, which lets the pentium process more than one instruction per clock cycle.

- The addition both of data and code caches on chip is also a feature designed to 3) improve processing speed.

- A new advanced computing technique used in pentium is called the branch 4) prediction, the pentium makes an educated guess where the next instruction following a conditional instruction will be. This prevents instruction cache from running dry during conditional instructions.

- The pentium has 64-bit data bus. This means that it can perform data transfers with 5) an external device twice as fast as a processor with a 32 bit data bus.

#### Compare 80486 and 80586. Q.4

#### Ans.:

| Sr. No. | 80486                                          | 80586 (Pentium I)                    |

|---------|------------------------------------------------|--------------------------------------|

| 1.      | It is 32 bit Microprocessor.                   | It is 64 bit microprocessor.         |

| 2.      | It's operating speed — 25 to 50 MHz            | It has 50 — 100 MHz operating speed. |

| 3.      | It has 32 bytes cache memory.                  | It has 8 kbytes cache memory.        |

| 4.      | It has external math co-processor.             | It has Internal math co-processor.   |

| 5.      | It was evolved in 1989-SX and 1991-DX version. | It was evolved in 1993.              |

# (Mar.03, 2011, Oct.04)

(Oct. 2011; March 2019)

(March 12, 19

#### Q. 5 Compare any four attributes of 486 DX with Pentium Processor.

Ans.:

| Attributes            | 80486 DX                     | Pentium                      |

|-----------------------|------------------------------|------------------------------|

| Data bus              | It is 32 bit microprocessor. | It is 64 bit microprocessor. |

| Operating speed (MHz) | Clock frequency 25-50 MHz    | Clock frequency 50 - 100 mF  |

| Introduction date     | It was evolved in 1991.      | It was evolved in 1993.      |

| Instruction Cache     | It has 32 bytes memory.      | It has 8 Kbytes memory.      |

#### Compare any four attributes of 80386 & Pentium processor. O. 6

Ans.:

|     | Attribute               | 80386                        | Pentium                     |

|-----|-------------------------|------------------------------|-----------------------------|

| (1) | Data bus                | It is 32 bit microprocessor  | It is 64 bit microprocessor |

| (2) | Instruction cache       | It has 16 byte cache memory  | It has 8 Kbyte cache        |

| (3) | Data cache              | It's data cache is 256 bytes | It's data cache is 8 Kbyte  |

| (4) | Math co-processor       | It has external co-processor | It has internal co-processo |

| (5) | Internal data word size | Word size is 16 bit          | Word size is 32 bits        |

| (6) | Introduction data       | It was introduced in 1985    | Introduced in 1993          |

| (7) | Operating speed in MHz  | 16-50 MHz                    | 50-100 MHz                  |

List the advanced microprocessors of INTEL X-86 family and mention three Q.7 (Oct. 03) attributes of any one of them.

34-

Vinde - 8051

(Mar. 06, 10, 20, Oct. 08, 10, July <sup>19)</sup>

Sugar

Ans.: List of INTEL X-86 microprocessors family :

- 8086

- 80286

- 80386

- .80486 .

- INTEL PENTIUM

- PENTIUM II

- PENTIUM III

- PENTIUM IV

For writing attributes of anyone of above please refer Q. No. 3.

Explain the advantages of the pentium processor with respect to the following Q. 8 features :

- 1) Dual pipelining 2) On-chip caches

- 3) Branch prediction 4) 64-bit data bus

Ans.:

Dual pipelining : 1)

The use of super scalar architecture incorporates a dual-pipelining in pentium processor, which lets pentium to process more than one instruction per clock cycle and achieve a high level of performance.

visit tpspoint.com for all chapters

(Mar 2010)

# 2) On-chip caches :

The data and code on-chip caches improves the processing speed of the pentium processor.

3-6

# 3) Branch prediction :

# The advantage of branch prediction is that, using it, the pentium makes an educated guess where the next instruction following a conditional instruction will be.

ii) This prevents the instruction cache from running dry during conditional instruction.

# 4) 64-bit data bus :

- i) Pentium has 64 bit data bus which allows higher speed of data transfer to it.

- ii) The data transfer speed of pentium is twice as fast as a processor with 32-bit data bus.

# Q.9 Compare any four attributes of 80286 and Pentium microprocessor. OR State four differentiating features among any two X86 family microprocessors. (March 2004, 2010, Oct. 2006)

Ans. :

| Attributes            | 80286                                                   | Pentium                                                |

|-----------------------|---------------------------------------------------------|--------------------------------------------------------|

| Database              | It is a 16-bit microprocessor.                          | It is a 64-bit microprocessor.                         |

| Address bus           | Address bus is 24-bit hence<br>can access 16 MB memory. | Address bus is 32-bit hence can<br>access 4 GB memory. |

| Operating speed (MHz) | Clock frequencies 6 MHz<br>to 20 MHz.                   | Clock frequencies<br>50 MHz to 100 MHz.                |

| Memory management     | External                                                | Internal                                               |

| Math co-processor     | External                                                | Internal                                               |

Q. 10 Compare any four attributes of 80286 and 80486 Processors.

(March 2013; July 18)

Ans.:

| Attributes              | 80286      | 80486     |

|-------------------------|------------|-----------|

| Data bus                | 16 bits.   | 32 bits   |

| Address bus             | 24 bits    | 32 bit    |

| Operating speed         | 6-20MHz    | 25-50 MHz |

| Physical memory address | 16 M bytes | 4 G bytes |

| Internal data word size | 16 bits    | 32 bits   |

| Introduction data       | 1982       | 1989      |

# **Programming Model of X-86 Family**

# (Oct. 2009)

Q. 11 State any six advance features of X -86 Micropreocessor Family.

Ans: Advance features of X-86 Microprocessor family are as follows:

- 1) It is capable of performing various computing functions and making decisions to change the sequence of program execution.

- 2) It is very powerful computing device.

| Conrocessor - Adv                                                                                                                         |                                  |                      |                    |                      |                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------|--------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5                                                                                                                                         | anced mi<br>h perform            | cropro               | cessors            | are suj              | Coprocessor – Advanced microprocessors are supported by numeric coprocessor. It is separate CPU which perform arithmetic functions & triconometric functions.               |

| Operating System<br>system                                                                                                                | : Micropi                        | rocesso              | r work             | s with               | Operating System : Microprocessor works with multiuser & multitasking operating<br>system.                                                                                  |

| rtual Memory :                                                                                                                            | Advanced                         | l micro              | oproces            | sor su               | Virtual Memory : Advanced microprocessor supports virtual memory technique for                                                                                              |

| Microprocessor includes special instructions & internal h/w whic<br>or to write s/w without knowing how much memory is available.         | te or data.<br>Iudes spec        | cial inst<br>vine he | ruction:           | s &r int<br>h mem    | Microprocessor includes special instructions & internal h/w which allow a programm <sub>ar</sub> or to write s/w without knowing how much memory is available.              |

| Explain the prog                                                                                                                          | gramming                         | mode                 | I for 32           | 2-bit v              | Explain the programming model for 32-bit version of X-86 family with suitable diagram.                                                                                      |

| <ol> <li>The 8088 and 8086 defin<br/>advanced microprocessors.</li> </ol>                                                                 | 86 defines<br>cessors.           | s the ba             | se prog            | rammi                | <b>Ans.</b> : 1) The 8088 and 8086 defines the base programming model for the entire X-86 family of advanced microprocessors.                                               |

| The newer members of X-86 family have<br>faster, they use 32-bit registers instead o                                                      | rs of X-86<br>2-bit regis        | 5 family<br>sters in | y have<br>stead o  | greateı<br>f 16-bi   | The newer members of X-86 family have greater computing power because they are faster, they use 32-bit registers instead of 16-bit registers and they have advanced         |

| addressing techniques.<br>Following figure shows programming model for 32-bit<br>bit microprocessor family i.e. in 386, 486 and pentium.: | ues.<br>Iows prog<br>family i.e. | rammir<br>in 386,    | ng mode<br>486 anc | el for 3.<br>I penti | addressing techniques.<br>Following figure shows programming model for 32-bit version of X-86 family used in 32<br>bit microprocessor family i.e. in 386, 486 and pentium.: |

|                                                                                                                                           | 31                               | 16                   | 16'15 8            | 8'7 (                | 0 Name                                                                                                                                                                      |

|                                                                                                                                           | Ĺ                                | EAX                  | AH                 | AL                   | Accumulator (AX)                                                                                                                                                            |

|                                                                                                                                           |                                  | EBX                  | BH                 | BL                   | Base Index (BX)                                                                                                                                                             |

| с: 5<br>Q                                                                                                                                 |                                  | ECX -                | CH                 | CL                   | Count (CX)                                                                                                                                                                  |

| General                                                                                                                                   |                                  | EDX                  | ΗΠ                 | DL                   | Data (DX)                                                                                                                                                                   |

| Registers                                                                                                                                 |                                  | ESI                  | SI                 |                      | Source Index                                                                                                                                                                |

|                                                                                                                                           |                                  | EDI                  | IQ                 |                      | Destination Index                                                                                                                                                           |

|                                                                                                                                           |                                  | EBP                  | BP                 |                      | Base pointer                                                                                                                                                                |

|                                                                                                                                           |                                  | ESP                  | SP                 |                      | Stack pointer                                                                                                                                                               |

|                                                                                                                                           |                                  |                      | S                  |                      | Codesegment                                                                                                                                                                 |

|                                                                                                                                           | Seg                              | Segment              | SS                 |                      | Stack segment                                                                                                                                                               |

|                                                                                                                                           | geg                              | Register             | ES                 |                      |                                                                                                                                                                             |

|                                                                                                                                           |                                  |                      | DS                 |                      |                                                                                                                                                                             |

|                                                                                                                                           |                                  |                      | GS                 |                      |                                                                                                                                                                             |

|                                                                                                                                           | L                                |                      | FS                 |                      |                                                                                                                                                                             |

|                                                                                                                                           |                                  | EIP                  | II                 |                      | Instruction pointer                                                                                                                                                         |

|                                                                                                                                           | E                                | E Flag               | Flag H             | Flag L               | Flag register                                                                                                                                                               |

- 6) The second group of registers is the segment group. This group consists of code segment, stack segment and four data segment registers. The data segment registers are DS, ES, FS and GS. These are 16-bit registers. These registers manage operation with external memory. Address computations and data movements are performed here.

- The third set of registers consists of Instruction Pointer (I.P.) and flag register.

- Q.13 Draw neat labelled diagram and explain the programming model of 16-bit version of X-86 family with register set. (Oct. 02, Mar. 2005, 2010, July 2017, 18)

#### Ans.:

- 1) The 8088 and 8086 defines basic programming model for X-86 family.

- The 16-bit version for programming model is used in 16-bit microprocessors of X-86 family i.e. in 8088, 8086 and 80286.

- 3) The 16-bit version of programming model of X-86 family is shown in the following figure.

| General<br>Purpose<br>Registers | ( AX<br>BX<br>CX<br>DX | AH<br>BH<br>CH<br>DH | 7 (<br>AL<br>BL<br>CL<br>DL<br>SI | Accumulator<br>Base Index<br>Count<br>Data<br>Source index |

|---------------------------------|------------------------|----------------------|-----------------------------------|------------------------------------------------------------|

|                                 |                        | В                    | DI<br>P<br>P                      | Destination index<br>Base pointer<br>Stack pointer         |

| Segme<br>registe                |                        | . S                  | Ś                                 | Code segments<br>Stack segments<br>Data segments           |

|                                 |                        | Ι                    | P                                 | Instruction pointer<br>Flag register                       |

#### Programming model of 16-bit version of X-86 family

- As shown in above figure the programming model of 16-bit version of X-86 family consists of three register groups.

- 5) The first group contains 8-general purpose registers called A, B, C, D, SI, DI, SP and BP registers. AL, BL, .... indicates lower bytes and AH, BH, .... indicates higher bytes. The full 16-bit registers are referred as AX, BX, CX and DX, where X stands for extended SI, DI, BP, SP registers are always treated as 16-bit registers. These are pointer registers because they are used to point locations within a segment.

| Π   |  |

|-----|--|

| 1   |  |

| Se  |  |

| en  |  |

| Sci |  |

| er  |  |

| ž   |  |

| E   |  |

| Ö   |  |

| ŝ   |  |

|     |  |

3-9

- The second group of registers is the segment group of registers. This group consists of code segment, stack segment and two data segment registers. Operation with external memory. Address computations and data movements are performed here. 6

- The third group of registers consists of instruction pointer (IP) and flag register. 5

# Enlist the different flags provided by 8086 microprocessor. Q. 14

Ans.:

The microprocessor 8086 has 16-bit flag register with 9 active flags, which are shown in following figure

|     |    | 1441         | 141   |   |        |  |

|-----|----|--------------|-------|---|--------|--|

| 8   |    | (I I amothy) |       |   |        |  |

| 0   | >  | 3            | 5     |   |        |  |

|     | -  | 11           | 2     |   |        |  |

| C   | 4  | P            | 4     |   |        |  |

| ¢   | σ  |              | D     |   |        |  |

| 1   | 4  | (            | AC    |   |        |  |

|     | S  | ١,           | _     |   |        |  |

|     | 9  |              | N     |   |        |  |

|     | ~  |              | S     |   |        |  |

|     | 80 |              | TESZL |   |        |  |

|     | 6  |              | E     |   |        |  |

|     | 10 |              | DF    |   |        |  |

| ŝ   | 11 | i)<br>L      | OF    |   |        |  |

|     | 12 |              | 11    | ) |        |  |

| i,  | 13 | 2            | 11    | ) |        |  |

| 9-0 | 14 |              | 11    | ) | where, |  |

|     | 5  |              | 11    | ) | W      |  |

Cy - Carry flag,

P - Parity flag,

AC - Auxiliary carry flag,

Z - Zero flag,

S - Sign flag,

TF - Single step trap,

IF - Interrupt flag,

DF - direction flag

OF - over flow flag

# 2005 (March 2003, Draw a neat labelled diagram of flag register of X86 family. Q. 15

Ans.:

Hag register is used to store special results from data operations. The flag register of X86 family is shown in following figure.

| 31 18 17       | 16 | 15 | 14 | 13 | 14                   | 11     | DT   | 2 | ø |   | 0 | 5 | H |   | F | ŀ |

|----------------|----|----|----|----|----------------------|--------|------|---|---|---|---|---|---|---|---|---|

|                | ł  | -  |    |    |                      |        | 1000 | 1 | 1 |   | 1 | 1 |   |   | 6 | 5 |

| Reversed Ac VM | R  | 0  | ż  | 0  | N <sub>T</sub> IO PL | о<br>0 | Δ    | I | T | s | N | 1 | A | I | 2 | 2 |

where -

$C \rightarrow Carry flag (CF)$

$P \rightarrow Parity flag (PF)$

→ Auxilliary carry flag (AF) 4

$Z \rightarrow Zero flag (ZF)$

$S \rightarrow Sign flag (SF)$

$T \rightarrow Trap$  flag (TF)

I → Interrupt flag (IF)

$D \rightarrow String Direction flag (DF)$

O → Overflow flag (OF)